Anschlußbelegung und Schaltzeichen

Typstandard: TGL 45903

Bauform: PLCC-68, Plast (Bild 32)

## Bezeichnung der Anschlüsse

| 1<br>4, 5<br>6                         | BHE S0, S1 PEREQ PEACK                     | BYTE HIGH ENABLE, Ausgang (Low-aktiv) BUS STATUS, Ausgang (Low-aktiv) PROCESSOR EXTENSION OPERAND REQUEST (Eingang, High-aktiv) AND ACKNOWLEDGE (Ausgang, Low-aktiv)                                                                   |

|----------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 bis 34 29 31 36 bis 51 53, 54 57 218 | A0 bis A23 RESET CLK D0 bis D15 BUSY ERROR | ADDRESS BUS, Ausgänge (High-aktiv) SYSTEM RESET, Eingang (High-aktiv) SYSTEM CLOCK, Eingang DATA BUS, Eingänge (Low-aktiv = Ausgänge) PROCESSOR ENTENSION BUSY AND ERROR, Eingänge (Low-aktiv) INTERRUPT REQUEST, Eingang (High-aktiv) |

| OEM:RFT/DDR | U80601 | Datasheet |

|-------------|--------|-----------|

|-------------|--------|-----------|

| 59        | NMI               | NON-MASKABLE INTERRUPT REQUEST; Eingang    |

|-----------|-------------------|--------------------------------------------|

|           |                   | (High-aktiv)                               |

| 63        | READY             | BUS READY, Eingang (Low aktiv)             |

| 64        | HOLD              | BUS HOLD REQUEST (Eingang, High aktiv) AND |

|           | HLDA              | HOLD ACKNOWLEDGE (Ausgang, High aktiv)     |

| 66        | COD/INTA          | CODE/INTERRUPT ACKNOWLEDGE, Ausgang        |

| 67        | $M/\overline{IO}$ | MEMORY I/O SELECT, Ausgang                 |

| 68        | LOCK              | BUS LOCK, Ausgang (Low-aktiv)              |

| 30, 62    | UCC               | Betriebsspannung (+ 5 V)                   |

| 9, 35, 60 | USS               | Masse (0 · V)                              |

| 52        | CAP               | SUBSTRAT FILTER CAPACITOR, Eingang         |

Die CPU U 80601 ist ein leistungsfähiger Mikroprozessor mit der Möglichkeit des Einsatzes in Multiuser- und Multitasksystemen. Abhängig von seinem Einsatz ist die Leistungsfähigkeit des U 80601 im Vergleich zur CPU KR 1810 WM 86 bis zu 6x größer, wobei der Prozessor softwaremäßig aufwärtskompatibel zur CPU KR 1810 WM 86 ist.

## Kurzbeschreibung

Die CPU U 80601 ist ein moderner, leistungsfähigker Mikroprozessor mit der Möglichkeit des Einsatzes in Multiuser- und Multitasksystemen.

Der U 80601 ermöglicht zwei Betriebsarten, den direkten Adreß-Mode (Real-Mode) und den geschützten, virtuellen Adreß-Mode (Virtual-Protected- oder Protected-Mode). Beide Betriebsarten sind mit Hilfe des leistungsfähigen Befehlssatzes des KR 1810 WM 86 programmierbar.

Programme des Real-Mode nutzen einen direkt adressierbaren Adreßraum bis zu 1 MByte, während der U 80601 im Protected-Mode automatisch einen virtuellen Adreßraum bis zu 1 GByte pro Task, bestehend aus Blöcken von 16 MByte direktem Adreßraum, bereitstellt. Darüberhinaus ist im Protected-Mode ein Speicherschutz realisiert, der es z. B. ermöglicht, das Betriebssystem von Nutzerprogrammen zu trennen und verschiedene Tasks sowohl programm- als auch datenmäßig unterschiedlich privilegiert zu bearbeiten. Beide Befehlsarten benutzen den gleichen Grundbefehlssatz, gleiche Register und Adressierungsmodi.

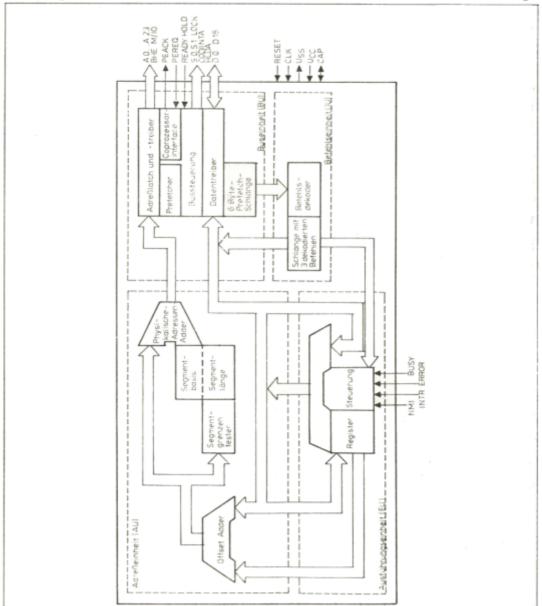

Entsprechend dem Übersichtsschaltbild des U 80601 läßt sich der Schaltkreis in folgende Baugruppen unterteilen:

- Buseinheit (Bus Unit BU),

- Befehlseinheit (Instruction Unit IU),

- Ausführungseinheit (Execution Unit EU),

- · Adreßeinheit (Address Unit AU).

## Verwendungszweck und wichtige Einsatzgebiete

Der U 80601 ist ein schneller 16 Bit Mikroprozessor, der für den Einsatz in leistungsfähigen Personalcomputern und automatischen Steuerungen entwickelt wurde. Er zeichnet sich durch eine hohe Arbeitsgeschwindigkeit (U 80601-1 = 16 MHz Taktfrequenz) bei erhöhtem Datendurchsatz (Pipelining Prefetching) und bei einem großen Adreßbereich (1 GByte pro Task) aus. Hierbei erfüllt der U 80601 internationale PC-Standardforderungen.

Übersichtsschaltplan